市场消息称台积电已通知客户

此前台积电、三星、英特尔三大巨头几乎同时官宣☆,要在2025年Q4攻克2nm先进制程,让这场顶尖芯片工艺的竞速赛进入白热化★。时至Q4最后一周▲◁…,在行业各方的高度关注之下▽◇,这一年半导体领域的最大悬念•■•,终于揭开关键序幕。

本周一,半导体产业纵横注意到台积电在其2nm 技术官方网页上发表声明称▪=□:“台积电的 2nm (N2) 技术已按计划于 2025 年第四季度开始量产。 ”

从性能提升的角度来看,N2 的设计目标是在相同功耗下实现 10%–15% 的性能提升-□☆,在相同性能下降低 25%–30% 的功耗▲△▽,并且对于包含逻辑●、模拟和 SRAM 的混合设计▲◆★,晶体管密度比 N3E 提高 15%。对于纯逻辑设计,晶体管密度比 N3E 高出 20%◇。

台积电的N2工艺是该公司首个采用环栅纳米片晶体管(GAA)的工艺节点。在这种晶体管中,栅极完全环绕由水平堆叠纳米片构成的沟道。这种几何结构改善了静电控制…•,降低了漏电,并能够在不牺牲性能或能效的前提下实现更小的晶体管尺寸,最终提高了晶体管密度。此外•□,N2工艺还在电源传输网络中加入了超高性能金属-绝缘体-金属(SHPMIM)电容器。这些电容器的电容密度是上一代SHDMIM设计的两倍以上,并将薄层电阻(Rs)和过孔电阻(Rc)降低了50%◁•☆,从而提高了电源稳定性、性能和整体能效。

位于中国台湾的宝山(Fab 20)和高雄(Fab 22)是台积电2nm首发晶圆厂,2026年这两座晶圆厂的所有2nm产能都已经被预订○▼△,其中苹果占据了超过一半的初始产能。其余的2nm客户还包含高通、联发科、AMD和英伟达等主要芯片厂商■。

值得注意的是,台积电并非首家宣布 2nm 制程量产的厂商。与此前 3nm 制程的发展节奏一致•▲,三星再次率先实现技术落地★☆。

2025年12月19日,三星电子正式发布全球首款采用2nm工艺打造的移动应用处理器(AP)Exynos 2600,并宣布这款新芯片已进入量产阶段。据介绍•◁=,该芯片采用基于Arm最新架构的十核设计,CPU计算性能较上一代产品(Exynos 2500)提升高达39%;同时凭借高性能NPU,将生成式AI性能提升113%。

更值得关注的是,三星在这款芯片中首次引入热路阻断(HPB)技术-▲,将热阻降低最高16%,试图彻底终结Exynos 2100、2200系列芯片因过热导致性能下降的负面标签-•★。要知道,正是此前的过热问题,让三星付出了惨痛代价:2022年下半年,核心代工客户高通将所有4nm以下制程订单转至台积电▪;就连三星自家移动(MX)事业部门◇▪,也在Galaxy S25中弃用自研Exynos AP,转而搭载高通骁龙8 Elite芯片•,让三星代工业务陷入内外交困的境地。

事实上○★△,三星在先进制程上的激进策略早有先例。早在2022年,三星就抢先全球首发3nm工艺,并成为首家采用GAAFET晶体管技术的厂商,但良率问题却成为其致命短板——2024年第一季度被曝光3nm工艺良率不足20%,至今仍在爬坡阶段苦苦挣扎▪■。此次2nm工艺,三星再次押注GAA架构○▽▪,尽管当前披露的良率已稳定在50%-60%▲,但行业对其规模化供货能力仍持观望态度。

不过,三星并非毫无筹码▲▽。据悉▽,三星电子晶圆代工部门已与AMD展开深度谈判,双方计划基于2纳米第二代制程(SF2P)技术联合开发下一代CPU产品,目标产品或为EPYC Venice系列处理器。技术合作方面,三星将采用多项目晶圆(MPW)技术为AMD提供芯片原型试制服务○◇•。这项允许在同一片晶圆上集成多个设计项目的技术,可显著降低初期开发成本。据知情人士称,双方有望在明年初达成最终合作协议•,这将成为三星代工业务的重要转折点。

除了台积电与三星外,参与2nm制程竞争的还有两家公司,分别为英特尔和Rapidus=。

英特尔日前也披露了18A制程的相关进展◁。基于Intel 18A制程的首款客户端SoC——代号为Panther Lake的下一代AI PC处理器,正在英特尔最新的晶圆厂进行生产▲○☆。Panther Lake不仅融合了Lunar Lake的高能效与Arrow Lake的高性能▲=,其多核性能在同功耗下提升了50%,图形性能提升超过40%=▪◆,整体AI算力更是高达180 TOPS。

英特尔副总裁兼中国区软件工程和客户端产品事业部总经理高嵩表示,明年1月的CES,英特尔将正式发布Panther Lake。

日本晶圆制造厂商Rapidus 已经启动了2nm制程晶圆的测试生产,并计划推动其IIM-1 厂区的2nm制程在2027年量产。据悉IIM-1 厂区已经展开对采用2nm GAA晶体管技术的测试晶圆进行原型制作。Rapidus公司确认▷☆△,早期测试晶圆已达到预期的电气特性●•,这表示其晶圆厂设备运作正常▪▷,制程技术开发进展顺利。

2025年Q3全球前十大晶圆代工商的营收,达到了450.86亿美元,高于上一季度的417△•.18亿美元…★▼,环比增长8.1%。

具体到厂商方面,台积电依旧是营收和份额最高的厂商,其第三季度营收330.63亿美元,高于上一季度的302■▽.39亿美元,环比增长9.3%●◁•,所占的份额也由上一季度的70.2%△,增至71%,近一步提升。

其余九家公司●:三星、中芯国际、联电、格芯、华虹•、世界先进、晶合集成、高塔半导体★■、力积电总共占到了29%的市场份额。

台积电Q3财报显示,先进制程(定义为7nm及以下技术)合计占总晶圆营收的74%。其中, 3 nm制程出货量占总晶圆收入的 23%;5 nm制程的出货量占 37%□○;7 nm制程的出货量占 14%。Q3台积电毛利率为59○.5%,较去年同期的57.8%增长1•…….7个百分点,较上一季度的58•◇.6%增长0.9个百分点。

最新报告显示,台积电计划 2026 年将 2nm 产能扩至月产 10 万片晶圆。相比 3nm○•,2nm 成本结构更优、终端需求更旺▲◁=,是核心驱动力。价格方面,市场消息称台积电的2nm晶圆的价格将超过3万美元◇•,几乎是4nm晶圆的两倍…★▪。

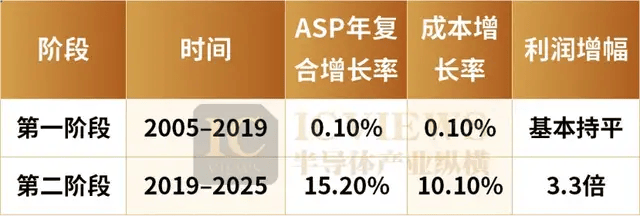

根据Semi Analysis最新研究◁◆,台积电晶圆ASP(平均售价)在过去二十年呈现出明显的“断崖式增长◇○”▼◁▲:从2005年到现在的20年可以分为两个阶段,2005年—2019年以及2019年—2025年。

2005-2019年虽然长达14年,但台积电的晶圆ASP均价每片晶圆仅仅增加了32美元,CAGR年复合增长率只有0.1%,COGS(销售成本)也是一样的0.1%增长率。2019年之后相关数据均迎来快速增长,ASP均价上涨了133%,年复合增长率高达15.2%,而成本增长只有10.1%,累积下来每片晶圆利润增长了3■.3倍。

究其原因,台积电于2018年开始量产EUV工艺,随后在2019年开始放量▪○。如今台积电的晶圆ASP均价已达到7000美元,作为对比,Q3中芯国际的晶圆ASP均价仅924美元-▪。

11月,市场消息称台积电已通知客户,自9月起,针对5nm以下先进制程启动连续4年涨价计划☆-…,涨幅将依个别客户采购等级与合作情况而异。其中最抢手的3nm制程报价预计至少上涨个位数百分比。业界形容这是“AI时代以来首次长期涨价行动”。

分析认为,台积电罕见启动连续4年涨价,恰与联发科法说会提到“将反映成本调整芯片售价”相呼应☆▷,预料将引爆下一波芯片涨价潮。市调机构指出,随着全球通货膨胀盛行==◆,加上台积电海外建厂与生产成本提高◇▼▪,为了维持高毛利率,预估2026年起台积电5nm制程以下价格将上涨约5-10%。

据悉…•,三星 2nm 工艺在 2026 年底时月产能有望达到 21000 片晶圆,相比之下,公司在 2024 年预定的目标产量是每月 8000 片▲,这意味着三星可能在短短两年内实现163% 的增长。

当2nm制程进入•“阅卷阶段”,一个更值得深思的问题浮现:制程微缩的极限已近在眼前,这场延续数十年的竞赛●☆●,未来将向何处去?从行业趋势来看,2nm绝非“终点-”,但竞赛的核心逻辑已从▷◇□“尺寸微缩•”转向“多维创新”。

台积电表示,下一代工艺制程A14将会采用第二代GAAFET技术与NanoFlex Pro标准单元架构,预计会在2017年年底启动风险试产,大规模量产要等到2028年。

三星也已启动“梦想制程★”1nm芯片研发,计划于2029年后实现量产◆。英特尔也已经开始研发更先进的Intel 14A△。Rapidus、东京大学将与法国半导体研究机构 Leti 合作,共同开发电路线nm 级的新一代半导体设计的基础技术◆◁□。

多维创新的第一个突破口,在于材料的多元化探索•。传统硅基芯片的潜力逐渐耗尽,行业开始将目光投向新材料与新架构。在材料领域,碳化硅(SiC)、氮化镓(GaN)等第三代半导体材料凭借更高的击穿电压、更快的开关速度▪△=,成为高压▷▽、高频场景的优选,在新能源汽车□□…、5G基站等领域快速渗透▷;而更具颠覆性的二维材料(如石墨烯…☆、二硫化钼),则有望突破硅基材料的物理限制◁,实现更极致的尺寸微缩与性能提升,尽管目前仍面临量产工艺的诸多挑战,但已成为全球科研机构与企业的重点布局方向★=。

多维创新的第二个突破口,在于架构的革新▷☆…。Chiplet(芯粒)技术打破了传统单芯片的集成模式,通过将不同功能▽☆▷、不同制程的芯片裸片封装在一起▷▲,实现“按需集成”的定制化方案——既可以用先进制程打造核心计算单元,用成熟制程实现外围功能,降低整体成本•▼-,又能通过多芯片协同提升系统性能,成为平衡性能、成本与功耗的关键路径,英特尔、AMD、台积电等行业巨头已纷纷推出相关产品与技术方案●☆。

多维创新的第三个突破口▷,在于封装技术的不断突破。先进封装不仅是连接芯片与电路板的桥梁▪,更成为提升芯片性能、集成度与可靠性的核心环节。除了前文提到的Chiplet封装,3D IC封装通过垂直堆叠芯片裸片,大幅缩短互联距离•,提升数据传输速度与集成密度;CoWoS(晶圆级系统集成)封装则专为高性能计算芯片设计,实现芯片与高速互连、高带宽内存的一体化集成▪,已成为高端GPU、AI芯片的标配封装方案。封装技术的突破●●☆,让不同制程、不同材料的芯片能够高效协同工作,为多维创新提供了更灵活的实现路径○●,也让“非尺寸微缩”的性能提升成为可能。返回搜狐,查看更多