在摩尔定律推动下,芯片设计的目标始终聚焦于

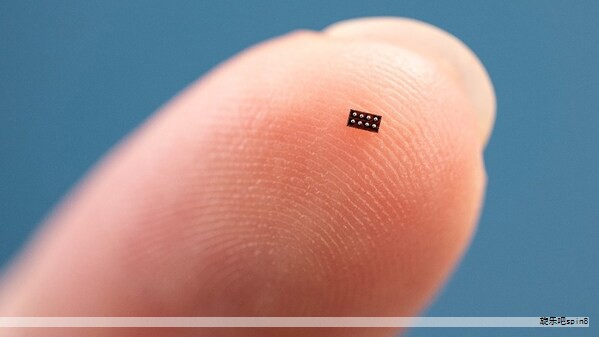

由于先进工艺研发成本居高不下、市场需求快速变化带来应用碎片化,单一“大芯片”难以覆盖所有需求,且高成本与大面积带来的良率下降会推高整体成本。为继续推动摩尔定律,业界逐步转向多芯片异构集成,通过将多个芯片封装在同一系统中来提升集成度与性能,同时控制成本,从而形成面向众核异构的芯片系统。

芯片互联技术的核心内涵

走入众核时代,各大厂商普遍采用多芯片集成的路径来扩展系统能力,形成了几类核心互联方案:旋乐吧spin8

- 基板封装(MCM),通过基板走线实现芯片间互联,适用于短距离低功耗场景。

- 硅中介层(Si Interposer)方案,在多片芯片底部引入硅介层作为连接桥梁,苹果等厂商已采用此路。

- 嵌入式多芯互连桥技术(EMIB),在基板制造时嵌入带有多层布线的电桥,通过桥连接多个裸片,英特尔采用该方案。

行业高层观点也指向一个共识:未来的CPU设计将偏向“多芯片SoC”,生态系统需要更好地支持小体量芯片的协同工作与集成。

M1 系列与 UltraFusion 技术的示例

以苹果为例,M1、M1 Pro、M1 Max、M1 Ultra的芯片尺寸和晶体管数量各不相同。M1 Ultra通过将两颗M1 Max芯片高效拼接,获得更高的算力与带宽,形成一个更大尺度的SoC。该架构在核心数量、显存带宽与神经网络引擎等方面实现显著提升,整体性能远超单芯片方案的简单叠加。其互连技术被称为 UltraFusion,采用大量硅中介层直接连接裸片,不依赖外部电路。通过这种设计,芯片内的数据传输带宽可达到极高水平,内存通道也实现了大幅扩展,提供更高的内存带宽。

在多芯片互联的实操层面,单纯通过主板PCB连接两颗处理器会带来显著的延迟、功耗与体积上的权衡,因此更高效的封装级互联成为趋势。UltraFusion的核心思路是通过高密度、低间距的封装连接实现芯片间的近似“同芯片”的通信体验,提升整个系统的性能与能效。

英伟达、英特尔与AMD的路径选择

业内领军者普遍认为“小芯片与异构计算”是应对摩尔定律放缓的关键手段之一。此类思路在数据中心级别的处理器设计与系统级芯片中均有体现,具备显著的带宽与能效优势。以数据中心场景为例,跨芯片互连方案在提升吞吐、降低延迟方面具有明显优势,并为后续的异构计算提供了可扩展的基础。

芯片间互联的标准化之路与挑战

为推动跨厂商、跨架构的互通,行业涌现出多种互联技术的探索与标准化努力。诸多厂商在封装与互联层面持续推出创新技术,如用于芯片间高密度互联的嵌入式桥接技术、以及在不同封装基底上的多种实现形态。关键在于通过统一的连接标准,实现不同厂商、不同工艺、不同架构的芯片能够高效协同工作,提升系统级性能。

芯片级互联联盟与开放生态

全球行业巨头联合推进小芯片互联的统一标准,构建开放的生态体系,以实现高带宽、低延迟、低能耗、低成本的芯片互联能力。尽管联盟成员结构并非完全覆盖所有关键玩家,但从多方技术路线来看,统一标准的引入有望推动跨厂商、跨工艺、跨架构的兼容与协作,形成更加灵活的模块化设计与快速迭代能力。

在全球范围内,部分地区也在推动本地化的 Chiplet 标准与生态建设,以便更好地结合本土产业链优势,提升自主创新能力。开放的 Chiplet 生态系统被视为未来芯片发展的关键支撑,行业伙伴在统一标准下共同推动新一代高性能、低功耗、低成本的多芯片互联方案落地。

要点总结

- 摩尔定律催生的不是单一大芯片的无限扩张,而是通过多芯片异构集成来提升性能与效能比。

- 常见的互联路径包括基板封装、硅中介层、嵌入式互连桥等,各自有不同的成本、延迟与带宽权衡。

- 高度集成的多芯片架构需要高效的封装级互联与统一的接口协议,以实现跨厂商协同与生态开放。

- 领先厂商在设计中已将多芯片互联作为核心思路,并通过自研的互连技术与标准化尝试推动行业向更高的集成度迈进。

- 开放的 Chiplet 生态与统一的互联标准是未来实现高性能、低功耗芯片的重要基石,行业协同将决定新一代计算架构的成败。