在摩尔定律持续推进的背景下,集成芯片与芯粒

集成芯粒技术的定义与内涵

传统集成电路以大规模晶体管在单一硅衬底上的二维平面布局为特征。集成芯粒技术则通过先将晶体管等功能单元制作为独立的芯粒(Chiplet),再按照应用需求将这些芯粒通过半导体工艺组合、集成交付成最终芯片的方式来实现。芯粒指的是预先制造、具有特定功能、可组合的独立晶片,常见功能包括通用处理、存储、图形处理、加密引擎、网络接口等。

核心理念在于以芯粒的复用性与组合性为基础,通过将多个具备专门功能的芯粒整合,形成高性能与多功能性兼具的新型芯片架构。相较于单芯片制造,芯粒化方案突破了单芯片面积的制约,提升了集成密度与计算能力,并通过敏捷制造理念更好地平衡个性化与通用性的矛盾,为产业带来新的设计与生产路径。

白皮书对集成芯粒技术的要点

- 集成芯片采用系统工程学原理,成为提升集成电路性能的第三条路径,开启设计范式的新纪元。

- 相对传统单芯片设计,集成芯片在以下方面具备显著优势:

- 增大芯片尺寸,推动集成度与算力的持续提升;

- 打破传统封装互连带宽与瓶颈,提升整体性能;

- 通过芯粒级的IP复用与预制组合实现更为敏捷的设计流程;

- 更好地控制制造过程,降低缺陷率与成本;

- 支持多类型芯粒的融合,催生更多新型芯片形态。

集成芯粒的架构设计与关键挑战

采用自上而下的“分解-整合-集成”模式,芯粒的分解与组合都需要复杂且高效的优化过程。白皮书从架构布局与电路设计层面提出六项核心挑战:

1) 分解与组合难题

在芯粒分解阶段需在成本、 安全性、系统性能等约束下进行优化。人工分解难以覆盖全部设计空间,芯粒筛选与搭配也往往依赖经验与经验法,导致效率低下与优化深度不足。需发展自动化的芯粒分解与组合技术,以提升设计效率与最优性。

2) 芯粒间互连网络

片上网络与基板网络的设计涉及互连拓扑、路由策略与容错机制。需在通用性与性能之间取得平衡,路由算法需具备拓扑无关性、全局可达性、故障独立性与可扩展性,并通过冗余路径等结构提升容错性。

3) 多芯粒系统的存储架构

多芯粒系统的存储设计直接影响访存效能与功耗,需在多级存储组织与存储管理优化上进行深度创新,以提升访问效率并降低额外成本。

4) 芯粒互连的接口协议

芯粒接口覆盖物理层与完整协议栈两大层级,需实现与厂商、架构及制造工艺的解耦,确保跨厂商、异构互联的广泛兼容性与开放性。

5) 芯粒间高速接口电路

高速接口涵盖线性有线、无线与光电互连等多种形式。当前面临功耗、信道自适应、检测/校正与跨工艺迁移等方面的挑战,需要在能效、带宽与稳定性之间实现综合优化。

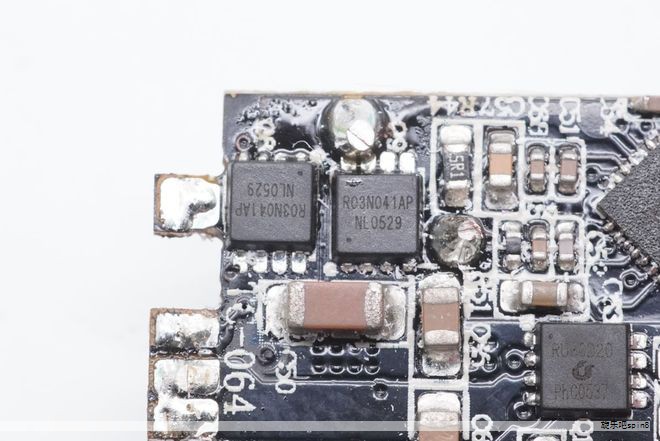

6) 集成芯片大功率供电电路

单颗高性能芯片的功耗已达百瓦级别,芯粒化扩大至大规模集成后,供电需求将显著提升。需在多级供电架构、供电网络与无源器件集成方面开展深入研究,确保稳定性、效率与体积的综合优化。

集成芯片的EDA与多物理场仿真需求

随着集成芯片规模的显著增大,对自动化设计方法与EDA工具的需求愈发迫切。关键方向包括:

- 系统级规划与分解组合的自动化

- 芯粒设计的协同化

- 硅基板(Interposer)与封装设计的集成化

- 3D协同优化设计

- 系统级验证与多物理场仿真

芯粒间互连的电磁仿真与版图自动化也面临挑战,随芯粒数量与类型的增加,互连数量激增,传统片上布线EDA工具在跨芯粒布线中的适用性下降,需发展针对分层互连的高效仿真与自动化布局技术。对芯粒尺度的电-热-力多场耦合仿真要求日益增强,需在热管理、电磁分布、应力与机械变形等方面提供统一的计算框架。

制造与散热工艺的要点

- 硅基板与RDL/Interposer制造

- 2.5D集成通常以硅基板为核心,通过微凸点和C4凸点实现芯粒与底部封装的电连接。大面积硅基板面临光罩尺寸限制、薄化处理、翘曲与拼接等工艺难题。高密度凸点键合面临对准精度、材料稳定性与边缘完整性的挑战。

- 高密度键合与集成工艺

- 芯粒之间的连接分为垂直通道(凸点、微凸点、混合键合界面)、水平导线以及硅通孔等三类。混合键合被视为打破10微米极限、实现亚微米级间距的关键路径,其优点包括降低对准误差带来的空洞风险、提升热稳定性,但仍需解决顶部金属-介质层的材料工程、划片精密性与整片无缺陷键合等难题。

- 散热与热管理旋乐吧spin8

- 芯片热管理经历逐层散热、芯片-热沉-外壳散热以及近结点冷却等阶段。随着封装复杂性与功率密度的提高,需在材料导热性、热膨胀匹配、电气性能及加工工艺之间实现协同优化,常在芯片级别引入微阀与微通道等散热组件,以应对高功率与高温区域的热负荷。

集成芯片面临的挑战与机遇

- 科学层面的核心问题

1) 芯粒的数学描述与组合优化理论

2) 大规模芯粒并行架构与设计自动化

3) 芯粒尺度的热-电-力耦合机制与界面理论

- 十项技术难题

1) 芯粒的抽象描述与模型化

2) 将复杂功能需求映射到大规模芯粒的分解与分配

3) 多芯粒并行体系结构与互连接口设计

4) 万亿晶体管级芯片的仿真与验证

5) 芯粒的测试、容错与可修复性

6) 万瓦级功耗芯片的散热与供电设计

7) 大尺寸有源/无源硅基板的架构与制造

8) 高速高密度连线的信号完整性挑战

9) 芯粒级热-力-电耦合仿真与相关工具

10) 大尺寸芯片的翘曲与力学稳定性问题

通过上述论述可以看出,集成芯片与芯粒技术在理论建模、自动化设计、热力电耦合仿真以及制造工艺等方面仍存在大量待解的难题,同时也在材料、器件与系统级设计层面展现出显著的创新潜力与发展的广度。