晶圆、晶粒、芯片、单元的概念与关系

- 晶圆(wafer):通过将高纯度单晶硅材料进行生长、拉晶、研磨、抛光与切割,得到圆形的硅片。晶圆是半导体制造的基底,承载后续的电路加工与器件形成。

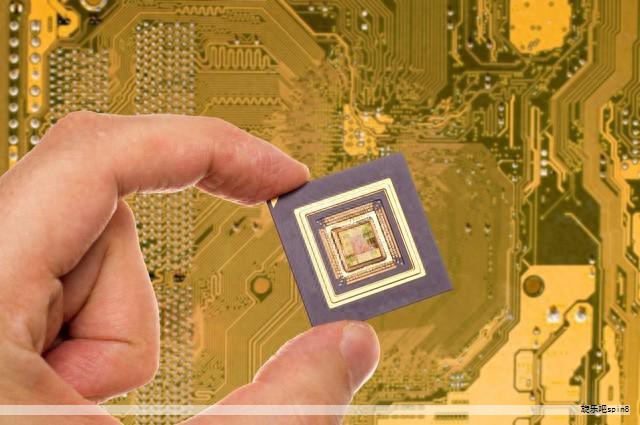

- 晶粒/裸芯片(die):晶圆上的一个最小加工单位,含有完整的电路结构但尚未封装,也没有引脚。一个晶圆上可以有大量的die,可能属于同一芯片,也可能是不同功能的芯片区域。

- 芯片(chip):经过封装并带有引脚的完整器件,能够对外提供电气连接和功能实现。

- 单元(cell):在电路设计中较小的功能单元,如一个逻辑门或一个乘法器等。一个cell可以指代不同层级的电路单元。

晶圆、晶粒与芯片的关系

- 批量制造特性:半导体制造采用大规模生产。一片晶圆上分布着大量die,多个晶圆一起进行加工。通常同一批次的晶圆上的die都是同一种芯片的不同实例,以实现高效、低成本的量产。

- 测试与分割:晶圆在生产过程中会对所有die进行测试,符合要求的die会切割下来并进入封装封测环节;不合格的部分则被废弃。

- 常见尺寸:晶圆的尺寸常见有6、8、12英寸等。

芯片制造过程的基本要点

- 相关术语简述:

- fabless:专注于芯片设计而不自设晶圆制造厂的公司。

- fab:晶圆制造厂,负责晶圆制造的环节,有时也称foundry。

- Foundry:代工厂,专注于制造、封装或测试中的某一环节,不包含设计。

- IDM:集成设备制造,芯片设计、制造、封装、测试及销售等环节一体化的企业模式。

- 制造流程的核心步骤(简要):先对晶圆进行清洗;在表面进行氧化和/或薄膜沉积;涂布光刻胶、曝光、显影;刻蚀、离子植入、金属沉积与溅射等反复工艺,逐层构筑多层电路与器件;最后完成晶圆级测试、分割、并进入封装与测试环节。旋乐吧spin8

- 2D芯片的特征:单层电路在晶圆表面逐层加工形成,最终通过多层光刻与加工实现完整的逻辑功能。

3D 与多层结构的演变

- 多层级的芯片封装与制造层级可分为三类:

- 2D(平面电路层):单层或多层在晶圆上逐层加工的电路结构。

- 伪3D/2.5D 封装:通过在不同芯片之间或芯片与基板之间使用中介层实现连接,通常包含RDL(再布线层)与中介层(interposer)。

- 3D/在一个芯片上实现多层级电路:直接在同一die上完成多层电路的堆叠,典型应用于某些闪存等存储器件。

- 常见的3D实现路径:

- 多die堆叠封装(通过 bonding 或 TSV 将多个晶粒封装在一起)。

- 在单一die上实现多层电路的制造,常见于高密度存储器件。

封装技术与关键概念

- 封装方式的基础对比:

- Wire bonding(引线键合):传统封装方式,成本低、工艺成熟,适合多 die 堆叠的场景,但引线长度和功耗存在局限性。

- Bump(凸点制造)与倒装焊(Flip-Chip):将金属凸点排列成二维矩阵,直接与封装底板连接,缩短信号路径、提升密度与性能。

- 3D 封装中的核心要素包括 bump pitch(凸点间距)以及下方金属层的可靠互连,数据传输点越密集,传输效率越高。

- UBM(Under Bump Metallization):凸点下金属层,主要作用是提供互连粘接、阻止材料扩散、以及保护介电层免受污染,确保凸点与下层金属之间的可靠连接。

- ReDistribution Layer(RDL,重新布线层)

- 通过在晶圆上增加一层或多层介质与金属层,将原有触点重新排列并延展至更适合的区域,以实现与凸点的有效连接。

- Interposer(中介层)

- 位于晶粒与基板之间的导电层,用于放大连接面、实现不同 die 的多重连接,是实现多 die 叠层连接的重要介质。

- 封装层级的演进与应用

- 当芯片面积较大时,单 die 的封装难度与成本提升,RDL、UBM、Interposer 等技术被广泛应用于2.5D与3D封装,以提升连接密度与性能表现。

- CoWoS(Chip-on-Wafer-on-Substrate)等先进封装技术实现了在晶圆、晶粒与基板之间的高密度、低损耗互连,广泛用于高端计算与显存应用。

总结要点

- 晶圆是一批量生产的基础底物,包含大量die;die是晶圆上的独立电路单元,尚未封装;chip是完成封装并具备外部连接的完整器件;cell是更小的基本电路单元。

- 现代芯片制造强调大规模、低成本的生产模式,通常同一晶圆上的die为同一芯片的不同实例,经过测试合格后进入封装与测试阶段。

- 芯片的层级与封装技术正在向2.5D、3D方向发展,通过RDL、Interposer、UBM、Bump等技术实现更高密度、更低功耗与更高性能的互连。